FET Yükselteçlerde Frekans Arttıkça Kazanç Neden Değişir?

FET Yükselteçlerde Frekans Etkisi: Devre Neden Değişir?

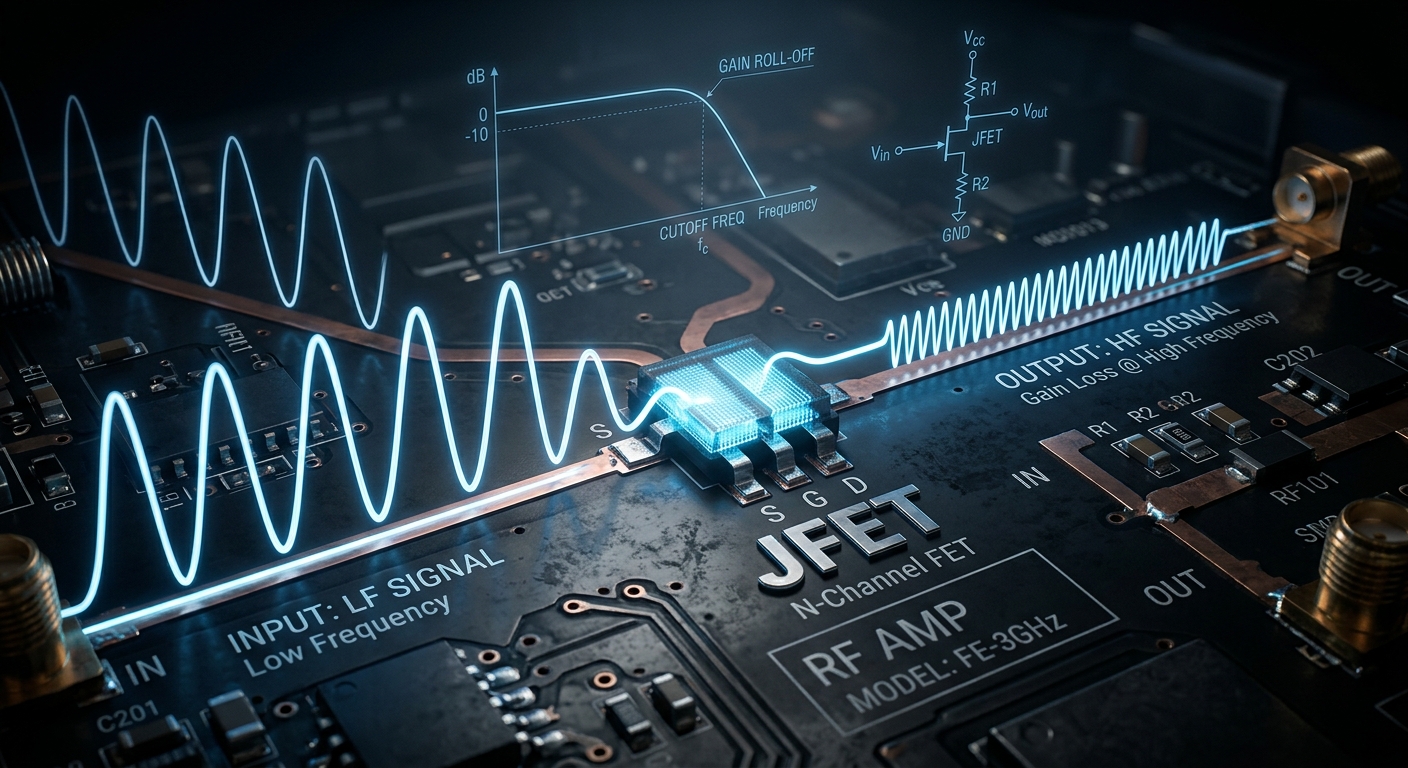

Elektronik tasarım dünyasında kağıt üzerindeki hesaplamalar, frekans işin içine girdiğinde her zaman beklenen sonucu vermeyebilir. Özellikle FET yükselteçlerde, 500 Hz gibi düşük frekanslarda stabil olan bir kazanç, 100 kHz seviyelerine çıkıldığında aniden düşmeye başlayabilir.

Peki, devre elemanları aynı kalmasına rağmen bu değişim neden yaşanıyor? Cevap, devrenin aniden bozulması değil; elemanların frekans değişimine karşı farklı roller üstlenmeye başlamasıdır. Frekans, FET katının iç dengesini her saniye yeniden kurar.

Düşük Frekansta Kazanç Neden Zayıflar?

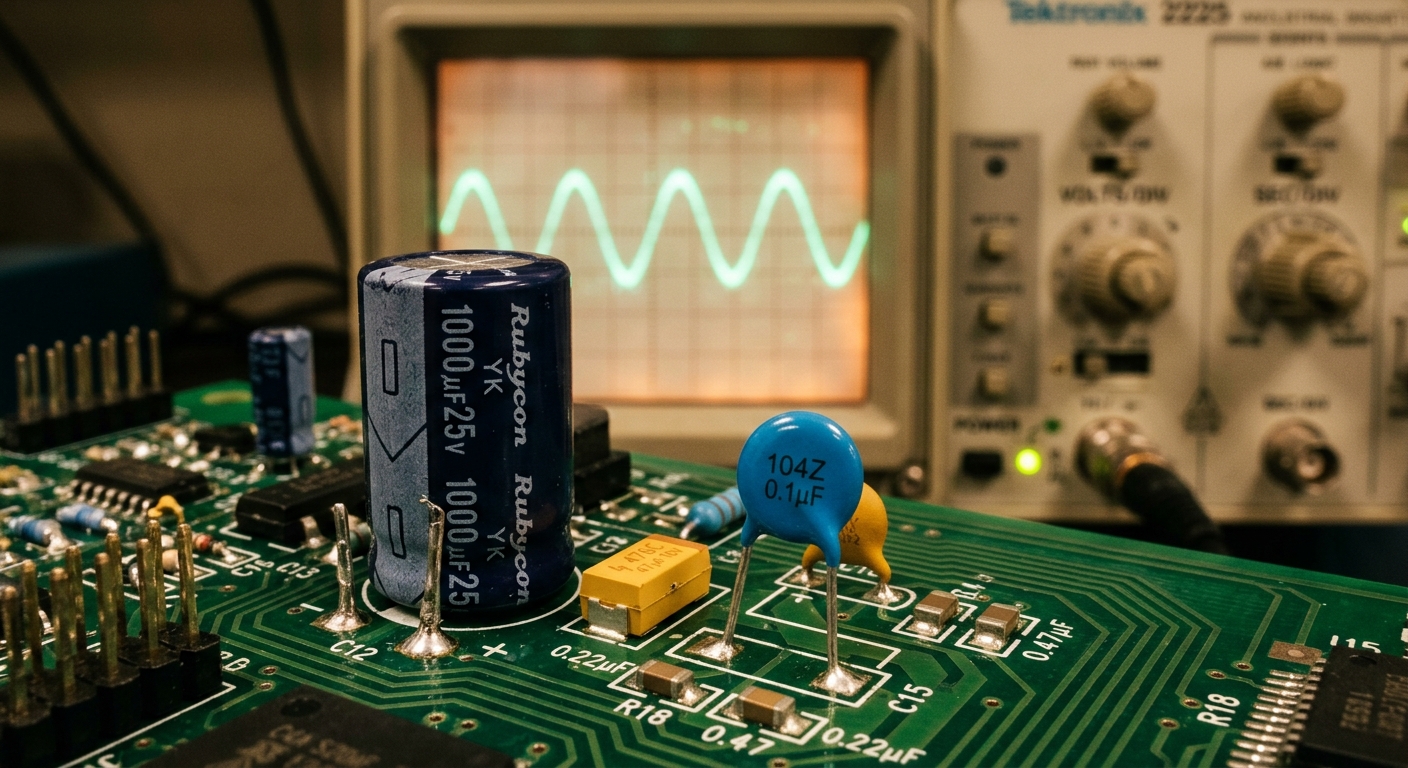

Düşük frekans bölgesinde en büyük engelleyiciler, devrenin giriş ve çıkışında bulunan bağlama kondansatörleri ile source bypass kondansatörüdür. Frekans düştükçe bu kondansatörlerin reaktansı (direnci) artar ve sinyal geçişi zorlaşmaya başlar.

Eğer bu kondansatörler yeterli kapasiteye sahip değilse, sinyal voltajının büyük bir kısmı kondansatör üzerinde harcanır. Bu durum, FET transistörünün kendisinden ziyade etrafındaki kondansatör mimarisinden kaynaklanan bir “daralma” etkisidir.

Özellikle hassas ses devreleri tasarlarken, alt kesim frekansını belirleyen bu zaman sabitlerine dikkat etmek gerekir. Daha fazla bilgi için JFET yükselteç temelleri içeriğimize göz atabilirsiniz.

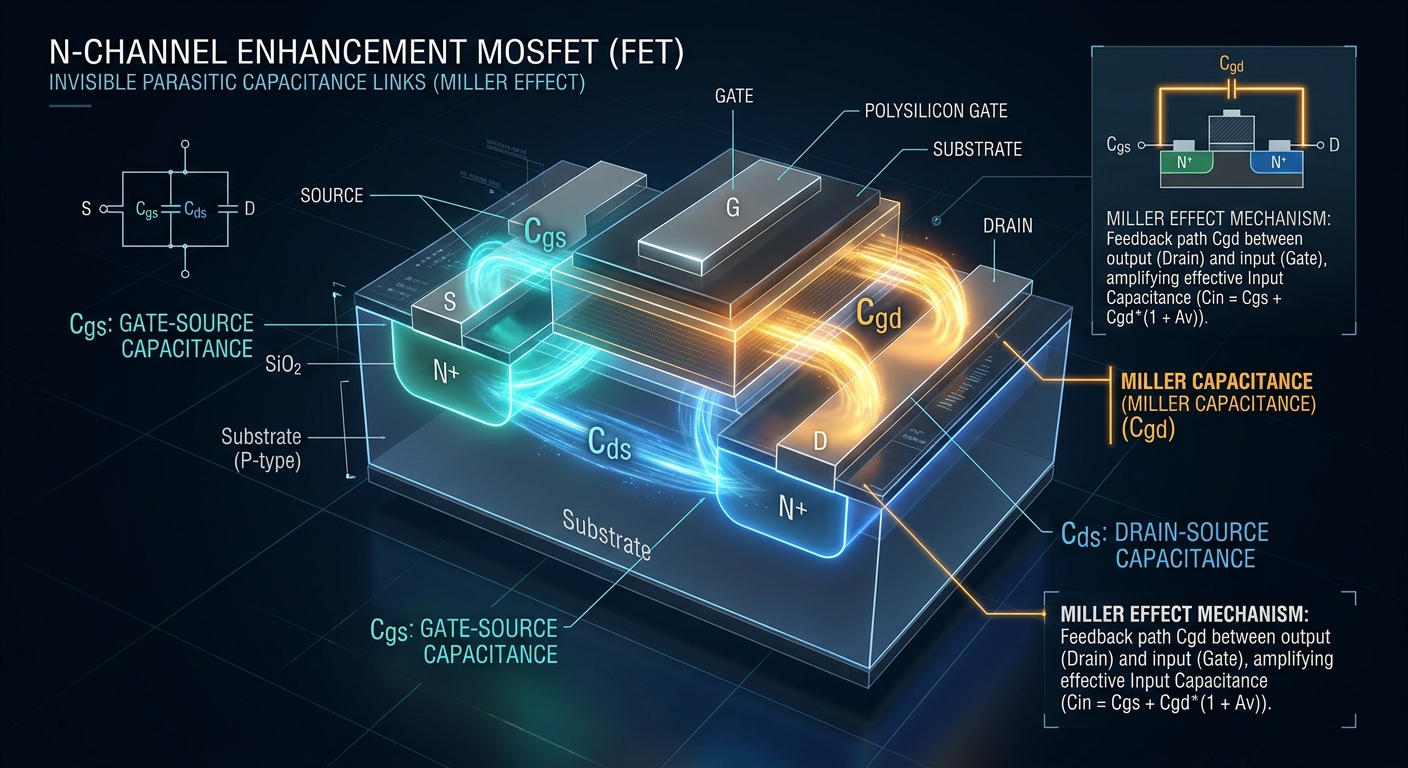

Yüksek Frekansta Gizli Düşmanlar: Parazitik Kapasiteler

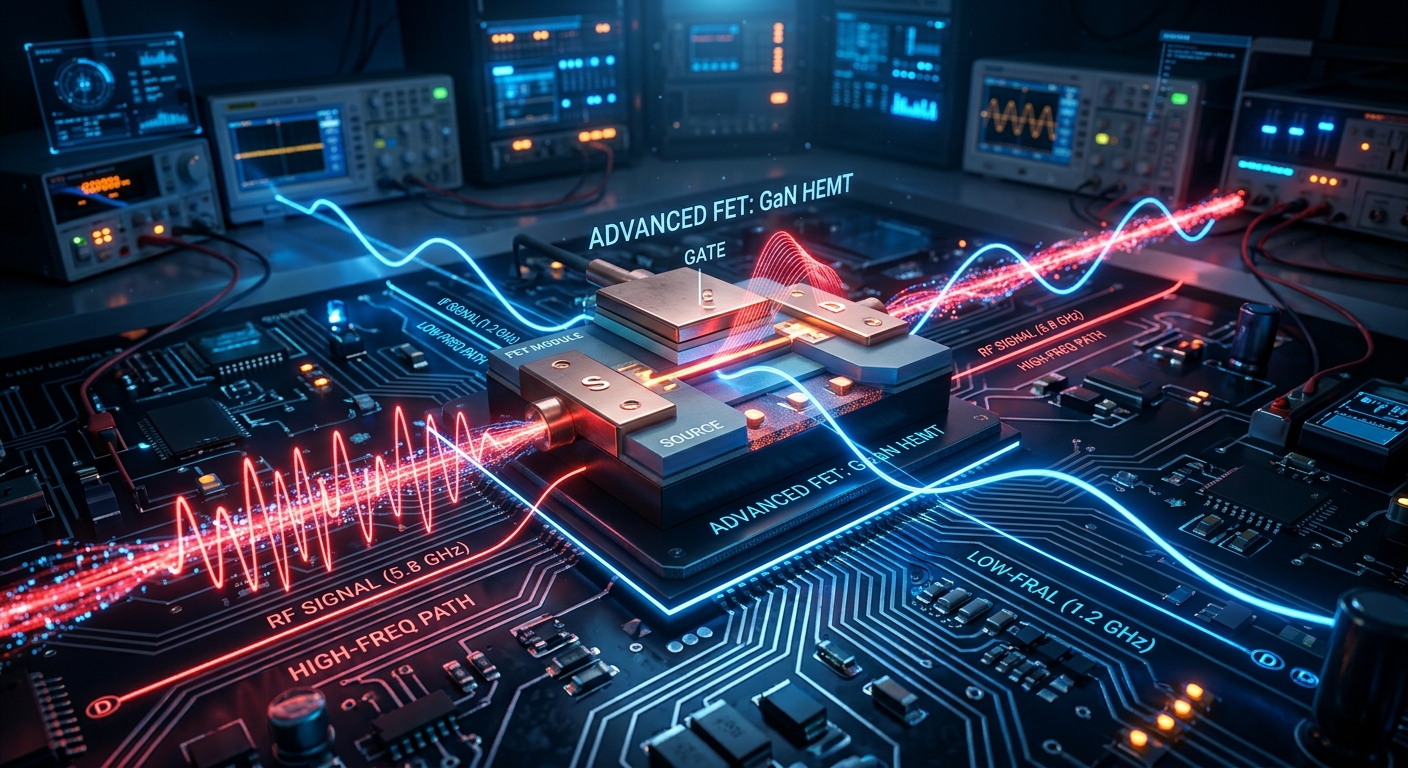

Frekans yükseldiğinde ise sahneye FET’in iç yapısından kaynaklanan gate-source (Cgs) ve gate-drain (Cgd) kapasiteleri çıkar. Bu küçük kapasiteler, düşük frekanslarda etkisiz olsa da yüksek frekanslarda sinyali şaseye sızdırmaya başlar.

Özellikle Miller Etkisi nedeniyle gate-drain kapasitansı, giriş katında olduğundan çok daha büyük bir yük gibi hissedilir. Bu “görünmez sis”, sinyalin kenarlarını yumuşatır, kazancı azaltır ve faz kaymasını artırarak devrenin çevikliğini bozar.

Drain Direnci (RD) Neden Hâlâ Önemli?

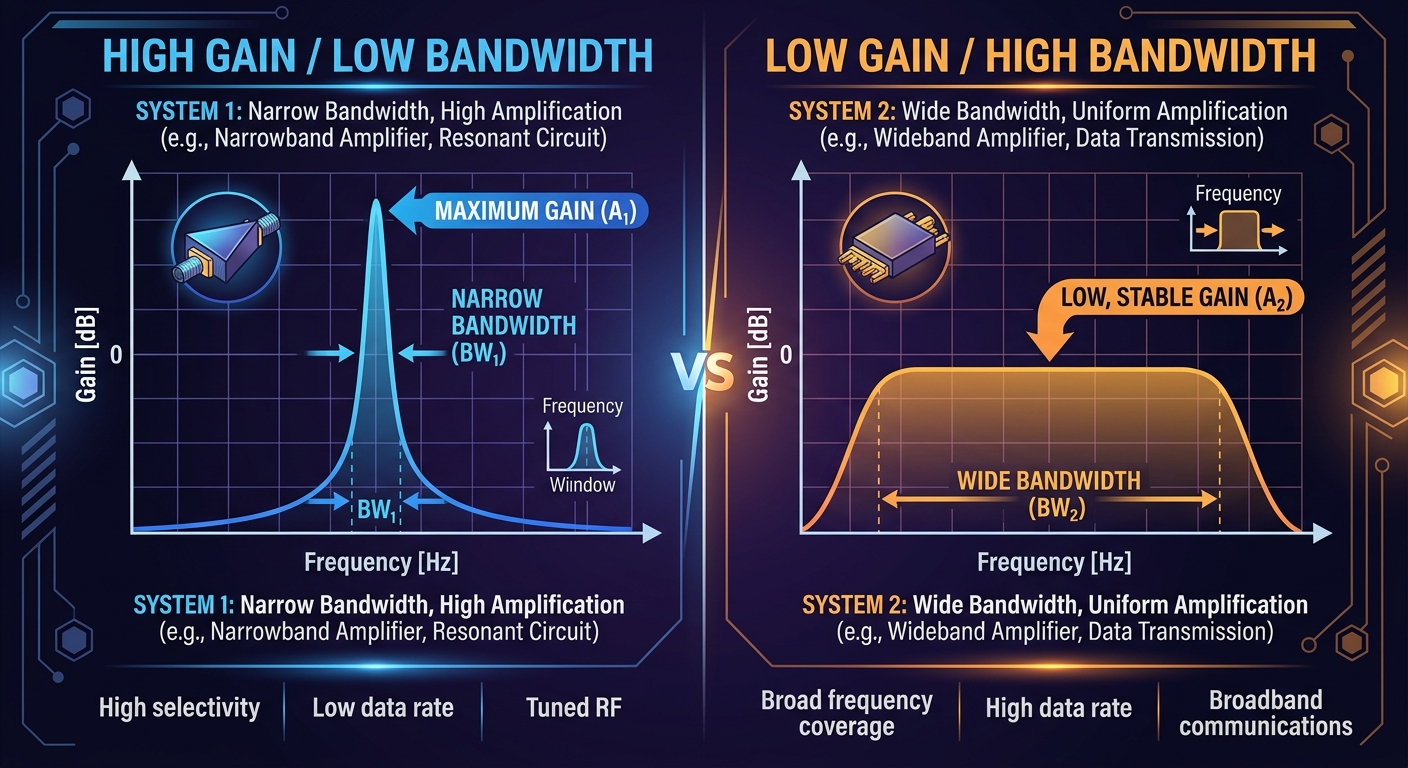

Drain direnci (RD), gerilim kazancının en temel oyuncularından biridir. RD değeri arttıkça kazanç yükselme eğilimine girer; ancak bu durumun bir bedeli vardır: Bant genişliğinin daralması.

Çok büyük bir RD direnci, teoride yüksek kazanç sunsa da pratikte devrenin lineer çalışma bölgesini daraltabilir. Bu nedenle frekans cevabını incelerken sadece kondansatörlere değil, RD seçiminin parazitik kapasitelerle nasıl bir etkileşime girdiğine de bakılmalıdır.

Frekans Taramasında Neyi Kaçırmamalı?

Bir FET katının performansını ölçerken alt ve üst frekans uçlarını ayrı ayrı analiz etmek en sağlıklı yöntemdir. Alt tarafta kondansatörlerin fiziksel kapasitesi, üst tarafta ise transistörün parazitik etkileri ve yerleşim kusurları (breadboard kapasitesi vb.) konuşur.

Eğer profesyonel bir tasarım yapıyorsanız, FET kullanılan osilatörler gibi yüksek frekans hassasiyeti olan devrelerde bu parametreleri mutlaka simüle etmelisiniz.

Sıkça Sorulan Sorular (SSS)

Soru: FET katında üst frekans sınırını en çok ne belirler?

Cevap: Genellikle gate-source ve gate-drain kapasiteleri ile devrenin fiziksel yerleşiminden gelen parazitik etkiler belirleyicidir.

Soru: RD direncini sonsuz artırarak kazancı artırabilir miyim?

Cevap: Hayır. RD arttıkça çalışma noktası kayar ve bant genişliği daralır; bu da devrenin yüksek frekanslarda tamamen işlevsiz kalmasına neden olabilir.

Son Not

Frekans arttıkça devrenin aynı kaldığını varsaymak, elektronikte yapılan en yaygın hatalardan biridir. FET yükselteçler, her frekans aralığında farklı bir karakter sergileyen dinamik yapılardır. Başarılı bir tasarım için bu “görünmez” etkileri yönetmeyi öğrenmek gerekir.

Siz de projelerinizde FET kullanırken frekans kaynaklı kazanç kayıplarıyla karşılaştınız mı? Deneyimlerinizi ve sorularınızı yorumlarda bizimle paylaşın!